社区微信群开通啦,扫一扫抢先加入社区官方微信群

社区微信群

社区微信群开通啦,扫一扫抢先加入社区官方微信群

社区微信群

Cyclone IV系列是业界成本最低、功耗最低的FPGA。采用该系列可以降低系统总成本的。

Cyclone IV 系列有两种不同的型号:

适用于多种通用逻辑应用的Cyclone IV E FPGA;

具有8个集成3.125-Gbps收发器的Cyclone IV GX FPGA。

表1-1注释:(1) 管脚列表文件中的用户I/O管脚包括所有的通用I/O管脚、专用时钟管脚以及两用配置管脚。收发器管脚和专用配置管脚不包括在这一管脚列表中。

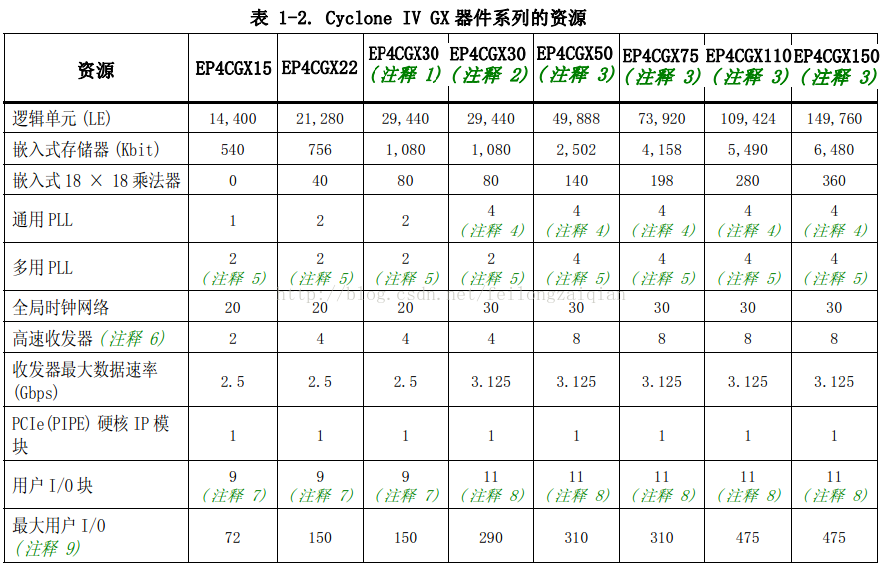

表1-2注释:

(1) 应用于F169和F324封装。

(2) 应用于F484封装。

(3) 仅有两个多用途PLL可应用于F484封装。

(4) 其中两个通用PLL可以支持收发器时钟。欲了解详细信息,请参阅 Clock Networks and PLLs in Cyclone IV Devices章节。

(5) 当多用PLL未用于同步收发器时,可将它们用于通用时钟。有关详细信息,请参阅 Clock Networks and PLLs in Cyclone IV Devices章节。

(6) 如果PCIe×1,您可以将该象限中其它收发器用于相同或者不同的数据速率下的其他协议。

(7) 包括用于HSSI参考时钟输入的一个配置I/O块和两个专用的时钟输入I/O块。

(8) 包括用于HSSI参考时钟输入的一个配置I/O块和四个专用的时钟输入I/O块。

(9) 管脚列表文件中的用户I/O管脚包括所有的通用I/O管脚、专用时钟管脚以及两用配置管脚。收发器管脚和专用配置管脚不包括在这一管脚列表中。

Cyclone IV器件系列具有以下特性:

■ 低成本、低功耗的FPGA架构:

■ 6 K到150 K的逻辑单元

■ 高达6.3 Mb的嵌入式存储器

■ 高达360个18×18乘法器,实现DSP处理密集型应用

■ 协议桥接应用,实现小于1.5 W的总功耗

■ Cyclone IV GX器件提供高达八个高速收发器以支持:

■ 高达3.125 Gbps的数据速率

■ 8B/10B编码器/解码器

■ 8-bit或者10-bit位物理介质附加子层(PMA)到物理编码子层(PCS)接口

■ 字节串化器/解串器(SERDES)

■ 字对齐器

■ 速率匹配FIFO

■ 公共无线电接口(CPRI)的TX位滑块

■ 电路空闲

■ 动态通道重配置以实现数据速率及协议的即时修改

■ 静态均衡及预加重以实现最佳的信号完整性

■ 每通道150 mW的功耗

■ 灵活的时钟结构以支持单一收发器模块中的多种协议

■ Cyclone IV GX器件对PCI Express (PIPE)(PCIe)Gen 1提供了专用的硬核IP:

■ ×1,×2,和×4通道配置

■ 终点和根端口配置

■ 高达256-byte的有效负载

■ 一个虚拟通道

■ 2 KB重试缓存

■ 4 KB接收(Rx)缓存

■ Cyclone IV GX器件提供多种协议支持:

■ PCIe (PIPE) Gen 1×1,×2,和×4 (2.5 Gbps)

■ 千兆以太网(1.25 Gbps)

■ CPRI (高达3.072 Gbps)

■ XAUI (3.125 Gbps)

■ 三倍速率串行数字接口(SDI)(高达2.97 Gbps)

■ 串行RapidIO(3.125 Gbps)

■ Basic模式(高达3.125 Gbps)

■ V-by-One(高达3.0 Gbps)

■ DisplayPort(2.7 Gbps)

■ 串行高级技术附件(Serial Advanced Technology Attachment (SATA))(高达3.0 Gbps)

■ OBSAI(高达3.072 Gbps)

■ 高达532个用户I/O

■ 高达840 Mbps发送器(Tx), 875 Mbps Rx的LVDS接口

■ 支持高达200 MHz的DDR2 SDRAM接口

■ 支持高达167 MHz的QDRII SRAM和DDR SDRAM

■ 每器件中高达8个锁相环(PLLs)

■ 支持商业与工业温度等级

在全球竞争和经济因素环境下,当今高技术产品利润和销售在不断下滑,工程设计团队在向市场推出低成本产品方面承受了很大的压力。新产品研发面临两种不同的系统挑战:利用最新的技术和功能开发全新的产品,或者采用市场上已有的解决方案,以降低开发成本。

在当今对成本和功耗都非常敏感的 “绿色”环境下,对于高技术企业,第一种挑战意味着开发全新的产品,其功能是独一无二的,具有较低的价格以及较低的功耗。 对于第二种挑战,通常通过降低产品原材料(BOM) 中元器件的成本来降低现有成功产品的成本。设计团队的另一选择是重新设计产品,不是针对新功能,而是要大幅度的降低成本。

在目前的全球经济形势下,这些系统挑战都与第三种挑战有关:以更少的人员、更低的预算,在更短的时间内完成低成本新产品的研发。

FPGA 能够缩短新产品开发的面市时间,降低了产品整个生命周期中的总体拥有成本(TCO) 。

系统总成本 = 产品原材料(BOM)成本 + 电路板成本 + TCO

所有Cyclone IV FPGA只需要两路电源供电,简化了电源分配网络,降低了电路板成本,减小了电路板面积,缩短了设计时间。

Cyclone IV 系列有两种不同的型号:

具有8个集成3.125-Gbps收发器的Cyclone IV GX FPGA;

适用于多种通用逻辑应用的Cyclone IV E FPGA。

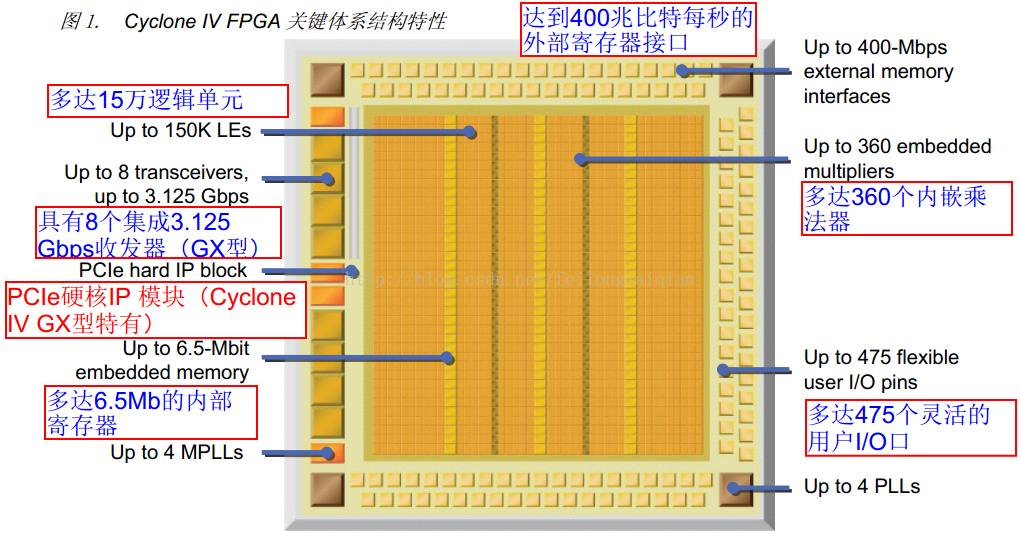

这些高速收发器支持多种串行I/O 协议,例如千兆以太网(GbE) 、PCI Express (PCIe) 、CPRI、XAUI、3G三速SDI 、Serial RapidIO®、SATA、DisplayPort 、V-b y-O n e 等,这些协议已经从前沿应用转变为主流应用。 Cyclone IV GX FPGA还含有嵌入式PCIe硬核IP 模块(图1),它不占用任何FPGA 逻辑,设计工程师使用它时能够比任何其他竞争FPGA 体系结构支持更多的功能。

Cyclone IV GX器件是唯一提供PCIe硬核IP 的低成本FPGA ,为根端口和端点提供x4支持。

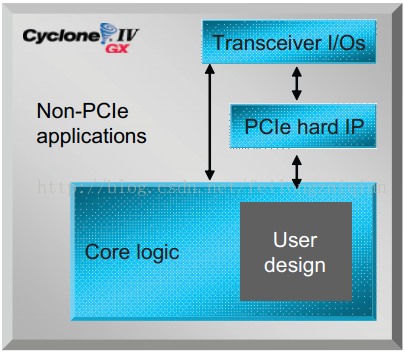

图6. Cyclone IV PCIe硬核IP 实现

Cyclone IV GX PCIe 硬核IP 模块的特性包括:

■ PCIe Gen1 性能

■ x1、x2、x4通路支持

■ 端点和根端口功能

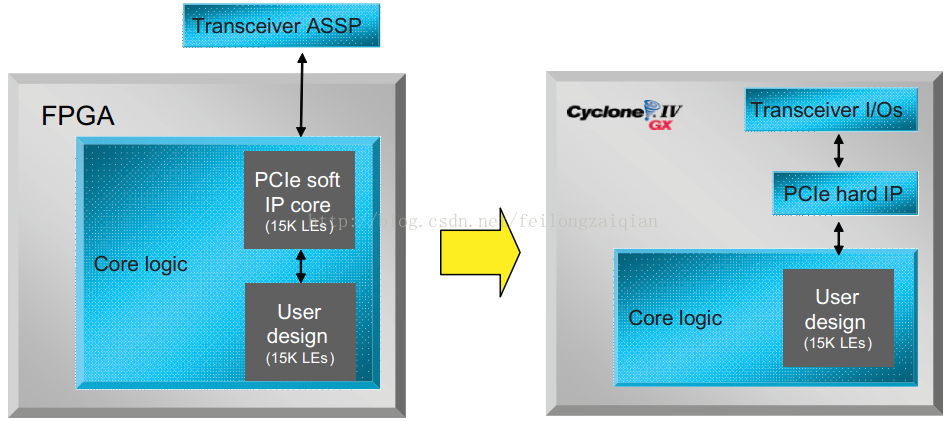

Altera®PCIe 硬核IP 模块节省的成本包括:

■ 不需要购买IP 内核(节省了TCO成本)

■ 比低成本FPGA 中其他的硬核IP 模块实现了更多的功能

■ 没有占用FPGA 逻辑,因此,可以使用更小、更便宜的FPGA (降低了 BOM成本 )(图7)。

图7. PCIe实现实例

Cyclone IV器件系列的速度等级

表1-6注释: (1) C8L、C9L和I8L速度等级适用于1.0 V的核电压。

(2) C6、C7、 C8、 I7和A7速度等级适用于1.2 V的核电压。

如果觉得我的文章对您有用,请随意打赏。你的支持将鼓励我继续创作!